# Electrical properties of Si/Si interfaces by using surface-activated bonding

Jianbo Liang, T. Miyazaki, M. Morimoto, S. Nishida, Naoteru Shigekawa

| Citation    | Journal of Applied Physics, 114(18): 183703                                        |  |  |

|-------------|------------------------------------------------------------------------------------|--|--|

| Issue Date  | 2013-11                                                                            |  |  |

| Type        | Journal Article                                                                    |  |  |

| Textversion | publisher                                                                          |  |  |

| Rights      | This article may be downloaded for personal use only. Any other use requires prior |  |  |

|             | permission of the author and AIP Publishing.                                       |  |  |

|             | The following article appeared in Journal of Applied Physics 114, 183703 (2013)    |  |  |

|             | and may be found at http://doi.org/10.1063/1.4829676                               |  |  |

| DOI         | 10.1063/1.4829676                                                                  |  |  |

Self-Archiving by Author(s)

Placed on: Osaka City University

# Electrical properties of Si/Si interfaces by using surface-activated bonding

J. Liang, T. Miyazaki, M. Morimoto, S. Nishida, and N. Shigekawa

Citation: Journal of Applied Physics 114, 183703 (2013); doi: 10.1063/1.4829676

View online: http://dx.doi.org/10.1063/1.4829676

View Table of Contents: http://aip.scitation.org/toc/jap/114/18

Published by the American Institute of Physics

## Articles you may be interested in

Surface activated bonding of silicon wafers at room temperature Applied Physics Letters **68**, 2222 (1998); 10.1063/1.115865

Effects of thermal annealing process on the electrical properties of p<sup>+</sup>-Si/n-SiC heterojunctions Applied Physics Letters **104**, 161604 (2014); 10.1063/1.4873113

Fast atom beam-activated n-Si/n-GaAs wafer bonding with high interfacial transparency and electrical conductivity

Journal of Applied Physics 113, 203512 (2013); 10.1063/1.4807905

Mechanisms for room temperature direct wafer bonding

Journal of Applied Physics 113, 094905 (2013); 10.1063/1.4794319

Effects of interface state charges on the electrical properties of Si/SiC heterojunctions

Applied Physics Letters 105, 151607 (2014); 10.1063/1.4898674

Bonding of silicon wafers for silicon-on-insulator

Journal of Applied Physics 64, 4943 (1998); 10.1063/1.342443

# Electrical properties of Si/Si interfaces by using surface-activated bonding

J. Liang, <sup>a)</sup> T. Miyazaki, M. Morimoto, S. Nishida, and N. Shigekawa *Department of Electrical Engineering, Osaka City University, 3-3-138 Sugimoto, Sumiyoshi-ku, Osaka 558-8585, Japan*

(Received 19 April 2013; accepted 24 October 2013; published online 11 November 2013)

Electrical properties of n-Si/n-Si, p-Si/n-Si, and  $p^-$ -Si/ $n^+$ -Si junctions fabricated by using surface-activated-bonding are investigated. The transmission electron microscopy/energy dispersive X-ray spectroscopy of the n-Si/n-Si interfaces reveals no evidence of oxide layers at the interfaces. From the current-voltage (I-V) and the capacitance-voltage (C-V) characteristics of the p-Si/n-Si and  $p^-$ -Si/ $n^+$ -Si junctions, it is found that the interface states, likely to have formed due to the surface activation process using Ar plasma, have a more marked impact on the electrical properties of the p-Si/n-Si junctions. An analysis of the temperature dependence of the I-V characteristics indicates that the properties of carrier transport across the bonding interfaces for reverse-bias voltages in the p-Si/n-Si and  $p^-$ -Si/ $n^+$ -Si junctions can be explained using the trap-assisted-tunneling and Frenkel-Poole models, respectively. © 2013 AIP Publishing LLC. [http://dx.doi.org/10.1063/1.4829676]

#### I. INTRODUCTION

Direct wafer bonding, in which two wafers are bonded to each other without adhesive or solder, has been widely applied for fabricating a variety of heterogeneous structures, such as Si/Si, Si/SiO<sub>2</sub>, Si/SiO<sub>2</sub>, GaAs/Si, InP/Si, GaAs/GaAs, and GaAs/InP<sup>7,8</sup> because it enables us to form junctions of semiconductor materials with different crystal structures or lattice constants. In almost all direct bonding methods-hydrophilic, hydrophobic, plasma-assisted bonding, and others 9-11—annealing after the bonding has been reported to be essential in achieving sufficient bonding strengths. 6–8,12 However, the fact that the need for annealing may limit the area of application of the direct wafer bonding, because the resultant thermal stress could cause the diffusion of doped impurities across the bonding interfaces. In addition, mechanical defects could occur at the bonding interfaces when junctions are made of materials with different thermal expansion coefficients.

On the other hand, surface-activated bonding (SAB), <sup>13–18</sup> in which substrates are attached to each other after their surfaces are activated by Ar plasma, <sup>13</sup> has been used for packaging semiconductor devices that are sensitive to thermal stress because there is no need to heat samples during the bonding process. Consequently, the mechanical and structural properties of SAB-based junctions have been investigated in the relevant research. <sup>15,16</sup> SAB is also applicable for fabricating junctions of dissimilar semiconductor materials with different thermal expansion coefficients as well as different crystal structures and lattice constants, and several results of *I-V* measurements have been reported for Si/Si, Si/InP, and Si/GaAs junctions fabricated by SAB. <sup>14,17,18</sup>

In this work, we fabricated n-Si/n-Si, p-Si/n-Si, and  $p^-$ -Si/ $n^+$ -Si junctions using SAB and performed I-V and C-V measurements to examine their electrical properties.

Mechanisms of carrier transport across the bonding interfaces in the p-Si/n-Si and  $p^-$ -Si/ $n^+$ -Si junctions were investigated by analyzing the ambient temperature dependence of their I-V characteristics. The structural properties of the bonding interfaces were examined by transmission electron microscopy (TEM) and energy dispersive X-ray spectroscopy (EDS) observations of the n-Si/n-Si junctions.

## **II. EXPERIMENTS**

#### A. Method

The n-Si/n-Si, p-Si/n-Si, and  $p^-$ -Si/ $n^+$ -Si junctions were made of four types (p-, n-,  $p^-$ -, and  $n^+$ -) of (100) Si substrates. Their carrier concentrations of the substrates, were estimated by Hall measurements at room temperature, are shown in Table I. To activate the sample surfaces, we used fast atom beams of Ar at the current of 1.8 mA and voltage  $\sim$ 2 kV for 180 s. After the bonding, ohmic contacts were prepared on the p- and  $p^-$ -type (n- and  $n^+$ -type) Si substrates by evaporating Al/Ni/Au (Ti/Au) multilayers on their backsides. The p- and  $p^-$ -type substrates were annealed at 400 °C for 60 s after the evaporation to obtain good contact characteristics. All the samples were diced into 4 mm<sup>2</sup> pieces.

*I-V* and *C-V* characteristics were measured with an ADCMT 6242 Source Measurement and an Agilent E4980A Precision Impedance Analyzer, respectively. The bonding interfaces of the *n*-Si/*n*-Si junctions were observed with TEM (Hitachi H9000UHR) equipped with an EDS apparatus.

#### **B.** Results

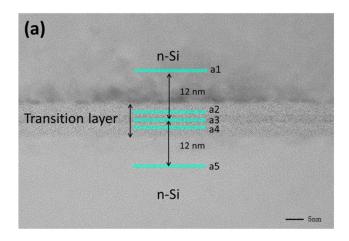

Figure 1(a) shows a TEM image of the n-Si/n-Si interface. A transition layer with thickness estimated to be 9 nm was formed at the interface. More importantly, no structural defects such as cracks were observed at the interface. Figure 1(b) shows EDS results for the upper n-Si substrate, inside the transition layer, and the lower n-Si substrate. The areas

a)Electronic email: liang@elec.eng.osaka-cu.ac.jp

TABLE I. The resistivity, the carrier concentration, and the thickness of substrates.

| Туре                    | Resistivity Ω·cm | Carrier concentration cm <sup>-3</sup> | Thickness cm |

|-------------------------|------------------|----------------------------------------|--------------|

| p-Si(100)               | 0.02             | $8.7 \times 10^{18}$                   | 0.0328       |

| n-Si(100)               | 0.02             | $2.5 \times 10^{18}$                   | 0.0328       |

| P <sup>-</sup> -Si(100) | 0.1              | $2.4 \times 10^{17}$                   | 0.0525       |

| n <sup>+</sup> -Si(100) | 0.002            | $2.6 \times 10^{19}$                   | 0.0525       |

for the respective EDS observations are marked a1, a2, a3, a4, and a5 in Fig. 1(a), where a2–a4 are inside of the transition layers and a1 and a5 are separated from the interface by approximately 12 nm. The atomic ratio of oxygen extracted from areas a3 (1.9%) and a4 (1.8%) are similar to that for area a1 (1.8%). The atomic ratio of oxygen for area a2

FIG. 1. (a) TEM cross-section image of the interface of n-Si/n-Si and (b) EDS composition maps of the interface of n-Si/n-Si.

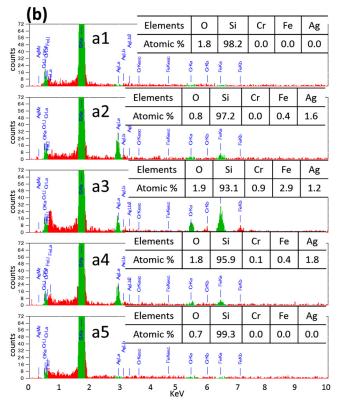

FIG. 2. *I-V* characteristics of *n*-Si/*n*-Si junction measured at room temperature.

(0.8%) is smaller than that for area a1 (1.8%), while it is close to that for area a5 (0.7%). Note that signals from Cr, Fe, and Ag atoms are observed in the EDS spectra for areas a2–a4. These elements are probably contaminants that formed during the activation process. No signals due to Ar atoms are observed in any of the EDS spectra.

Figure 2 compares the *I-V* characteristics of the *n*-Si/*n*-Si junctions with those of *n*-Si substrates with contacts on both surfaces, measured at room temperature. The *I-V* characteristics of both samples show excellent linearity and the discrepancy between their *I-V* characteristics is small. Similar results were recently reported for n-Si/n-GaAs junctions. <sup>19,20</sup> From a least square fitting, the resistances of the *n*-Si/*n*-Si junctions and the *n*-Si substrates were determined to be 0.17 and 0.16  $\Omega$ -cm<sup>2</sup>, respectively. The difference may be due to the differences in sample thicknesses and in the resistance across the bonding interfaces in the *n*-Si/*n*-Si junctions. These results indicate that the influence of a potential barrier across the bonded interface on the conductive properties, if any, should be small in comparison with that of the sum of the contact resistance and the resistance in the *n*-Si substrates.

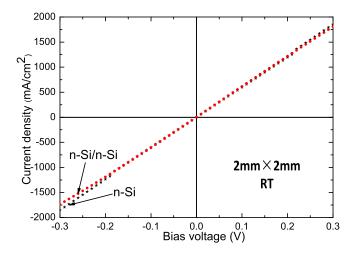

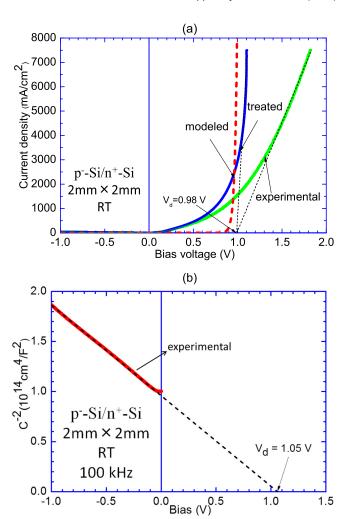

Figure 3(a) shows the I-V characteristics of the p-Si/n-Si junction, measured at room temperature. As is seen in the "as-measured" curves, the current for forward-bias voltages higher than 0.5 V is almost proportional to the bias voltages, which suggests that the conduction properties in this voltage region are dominated by parasitic resistance. We estimated the parasitic resistance from the slope of the curve and obtained the "treated" I-V characteristics by subtracting its contribution from the "as-measured" curve. The intrinsic electrical properties, or the properties at the bonding interfaces, are assumed to appear in the treated curve. We also calculated the I-V characteristics in the framework of a Schockley model using the reported dependence of the life time and mobility of the minority carriers on the concentration of the majority carriers. <sup>21,22</sup> The obtained *I-V* characteristics are labeled "modeled."

Both the as-measured and treated *I-V* characteristics reveal rectifying properties similar to those in conventional pn junctions. For both curves, the turn-on voltage is the

FIG. 3. (a) I-V and (b) C-V characteristics of p-Si/n-Si junctions measured at room temperature.

same,  $\sim 0.23$  V, which is surprisingly small compared to that of the modeled curve (0.95 V). The currents for reverse-bias voltages in the as-measured and treated *I-V* characteristics are larger than that of the modeled characteristics. The  $I/C^2$ -V characteristics of a p-Si/n-Si junction measured at 100 kHz are shown in Fig. 3(b), in which a marked warp is observed.

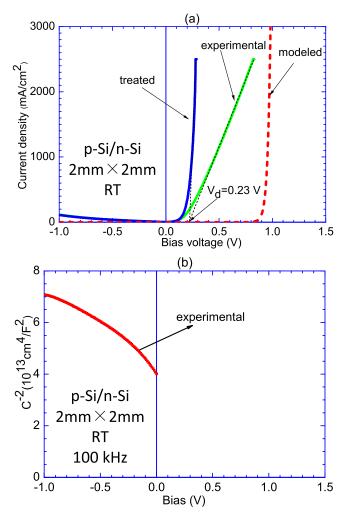

Figure 4(a) shows the as-measured, treated, and modeled curves of the I-V characteristics of the  $p^-$ -Si/ $n^+$ -Si junction, measured at room temperature. The as-measured and treated curves exhibit rectifying properties. In addition, the turn-on voltage is  $\sim 0.98$  V, which is close to that for the modeled curve (0.93 V). Figure 4(b) shows the  $I/C^2$ -V characteristics of the  $p^-$ -Si/ $n^+$ -Si junction measured at 100 kHz, the result is a straight line. Using its slope, the concentration of ionized acceptors in the  $p^-$ -Si substrate was estimated to be  $1.5 \times 10^{17}$  cm<sup>-3</sup>, which is close to that obtained from Hall measurement ( $2.4 \times 10^{17}$  cm<sup>-3</sup>). From the capacitance value, we also estimated the thickness of the depletion layer and obtained a value of approximately 100 nm at zero-bias voltage. The diffusion potential was found to be  $\sim 1.05$  V by linearly extrapolating  $1/C^2$  to zero.

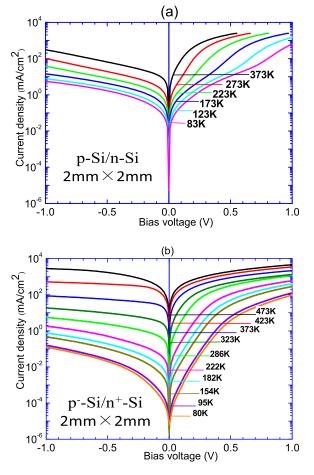

The *I-V* characteristics of p-Si/n-Si and  $p^-$ -Si/ $n^+$ -Si junctions measured at various temperatures are shown in

FIG. 4. (a) I-V and (b) C-V characteristics of  $p^-\text{-}Si/n^+\text{-}Si$  junctions measured at room temperature.

Figs. 5(a) and 5(b). Note that the magnitude of the current increases in both p-Si/n-Si and p<sup>-</sup>-Si/n<sup>+</sup>-Si junctions with increasing depth of the reverse bias. The magnitude of the current also increases with increasing temperature. We also find that the slope of the current for reverse-bias voltages between 0.3 and 0.75 V in the p-Si/n-Si junctions is not sensitive to the ambient temperature. The slope in the p<sup>-</sup>-Si/n<sup>+</sup>-Si junctions, in contrast, decreases as the ambient temperature increases.

# III. DISCUSSION

Noting that the characteristic X-ray signals in EDS measurements are generated in a region with a depth of a few micrometers, the scattering characteristics of the atomic ratio of oxygen among the a1, a2, a3, a4, and a5 areas might be attributable to possible fluctuations in the thickness of the native oxides formed on the side of samples exposed to air by dicing. This suggests that there is no oxide layer at the Si/Si interface, which is consistent the parasitic resistance's being larger than that across the interfaces in the *n*-Si/*n*-Si junctions (Fig. 2). The result is in large contrast to that for conventional wafer bonding, where the resistance across the bonding interfaces has been reported to be larger than their

FIG. 5. I-V characteristics of (a) p-Si/n-Si and (b)  $p^-$ -Si/ $n^+$ -Si junctions measured at various temperatures.

parasitic resistance,<sup>23</sup> presumably due to residual oxide layers formed at the interfaces achieved.<sup>6,8</sup>

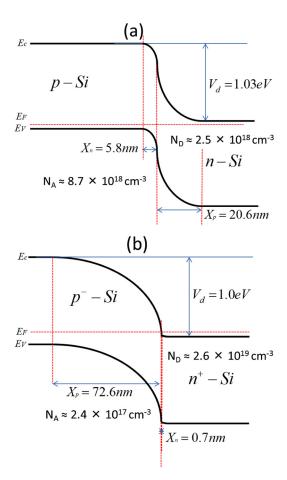

Figures 6(a) and 6(b) show energy-band diagrams of the p-Si/n-Si and  $p^-$ -Si/ $n^+$ -Si junctions, respectively, at zero-bias voltage and at room temperature. These diagrams are based on the carrier concentrations of the respective substrates shown in Table I. Note that these diagrams stem from the assumption that there are no additional charges located at the interfaces. The diffusion potentials are found to be 1.03 and 1.0 V for the p-Si/n-Si and  $p^-$ -Si/ $n^+$ -Si junctions, respectively. The total depletion layer thicknesses are estimated to be 26.4 and 73.3 nm for the p-Si/n-Si and  $p^-$ -Si/ $n^+$ -Si junctions, respectively.

For the p-Si/n-Si junctions, we observed a large discrepancy between the diffusion potential (1.03 V) and the turn-on voltage (0.23 V) in the I-V characteristics. Similar discrepancies reported for p-GaAs/n-GaN and p-SiC/n-GaN heterojunctions fabricated by wafer fusion. <sup>24–26</sup> In addition, a warp in the  $I/C^2$ -V characteristics, which we observed for the p-Si/n-Si junctions, has also been reported for n-Ge/p-Si diodes. <sup>27</sup> Such discrepancies between the turn-on voltages, the expected diffusion potential, and warps appearing in the  $I/C^2$ -V characteristics have been explained <sup>25–28</sup> by assuming that carriers tunnel through the possibly formed interface states and some of the carriers become trapped at such states so that the electrical charges are placed at the interfaces.

FIG. 6. Schematic energy-band diagram of (a) p-Si/n-Si and (b)  $p^-$ -Si/ $n^+$ -Si junctions.

In the present work, the Ar plasma irradiation in the SAB process is assumed to induce the interface states. Such interface states or traps should be distributed in the 9 nm thick transition layer [Fig. 1(a)], which was likely to be made due to the Ar plasma irradiation. Although the interface states are likely formed in p-Si/n-Si and p-Si/n+Si junctions during the Ar plasma irradiation, we observed marked discrepancies neither between the turn-on voltage and the diffusion potential nor between it and the warps in the  $I/C^2$ -V characteristics for the p-Si/n+Si junctions.

The difference mentioned above between the p-Si/n-Si and  $p^-$ -Si/ $n^+$ -Si junctions might be related to their depletion layer thicknesses: Given that the total thickness of the depletion layer in the p-Si/n-Si junctions, 26.4 nm at zero-bias voltage, is comparatively close to (approximately only three times as large as) the thickness of the transition layers, the characteristics measured for the p-Si/n-Si junctions are assumed to be more strongly influenced by the properties in the bonding interfaces. In the  $p^-$ -Si/ $n^+$ -Si junctions, in contrast, the depletion layers in the  $p^-$ -Si substrates, which are 72.6-nm thick at the zero bias voltage, are much thicker than the transition layers, while the depletion layers in the  $n^+$ -Si substrates, 0.7-nm thick at the zero bias voltage, are much thinner. It is assumed, consequently, that the impact of the properties of the bonding interfaces on the turn-on voltage and the  $I/C^2$ -V characteristics in the  $p^-$ -Si/ $n^+$ -Si junctions is smaller than in the p-Si/n-Si junctions.

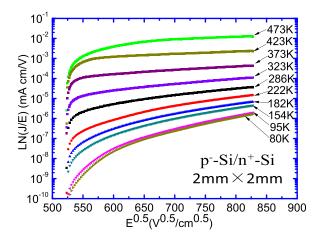

FIG. 7. Measured reverse-bias current density divided by electric field vs square root of electric field for  $p^-$ -Si/ $n^+$ -Si junctions at temperatures ranging from 473 to 80 K

The electrical properties in the n-Si/n-Si junctions are also assumed to be influenced by the states at the bonding interfaces. The results of measurements of I-V characteristics, however, suggest that their impact on the conductive properties is comparatively small in the n-Si/n-Si junctions.

In the *I-V* characteristics of the *p*-Si/*n*-Si junctions, the fact that the slope of the current for reverse-bias voltages between 0.3 and 0.75 V in the semi-log scale is not sensitive to the ambient temperature [Fig. 5(a)] suggests that the tunneling process dominates the transport of carriers across the interfaces. A numerical analysis has shown that the features of the *I-V* characteristics for reverse-bias voltages can be explained by the view of the trap-assisted tunneling through 0.2 eV traps, <sup>14</sup> which are assumed to be related to the interface states.

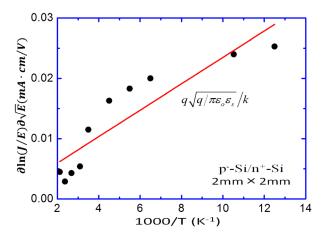

Figure 7 shows the relationships between the ratio of the current density (J) to the maximum electric field (E) in the junctions and the square root of E of the  $p^-$ -Si/ $n^+$ -Si junctions, which were extracted from their I-V characteristics for reverse-bias voltages. We find that the relationship between  $\ln(J/E)$  and  $\sqrt{E}$  is close to a straight line for E between 360 and 685 kV/cm ( $\sqrt{E}$  between 600 and 828 V<sup>0.5</sup>/cm<sup>0.5</sup>) at each temperature. The relationship between the slope of the lines  $(\partial \ln(J/E)/\partial \sqrt{E})$  obtained for the above electric field range and the inverse of temperature is shown in Fig. 8. Also shown is a straight line, which corresponds to

FIG. 8. Slope of the curves shown in Fig. 7 for the  $p^-$ -Si/ $n^+$ -Si junctions.

$$\partial \ln(J/E)/\partial \sqrt{E} = q(q/\pi \varepsilon_o \varepsilon_s)^{1/2}/k_B T,$$

(1)

where  $\varepsilon_o$  and  $\varepsilon_s$  are vacuum permittivity and the dielectric constant of Si, respectively. Each data point in this figure is placed along this line, which suggests that the transport properties of carriers in the reverse-biased  $p^-$ -Si/ $n^+$ -Si junctions can be semi-quantitatively explained using the Frenkel-Poole model, <sup>29,30</sup> as in the case of metalorganic chemical vapor deposition (MOCVD)-grown InGaN pn junctions. We actually confirmed (not shown) that the results of analyses using other models, such as the generation-recombination model, <sup>32</sup> band-to-band tunneling model, <sup>33</sup> field-emission tunneling model, <sup>34</sup> and trap-assisted tunneling model <sup>14</sup> are not in agreement with the measurements for the  $p^-$ -Si/ $n^+$ -Si junctions.

Similar to the difference in the turn-on voltage and  $1/C^2$ -V characteristics, the difference in the likely mechanisms that dominate the carrier transport for reverse-bias voltages between the p-Si/n-Si and the p-Si/n+-Si junctions might be related to the depletion layer thickness in the two junctions.

## IV. CONCLUSION

We investigated the electrical properties of n-Si/n-Si, p-Si/n-Si, and  $p^-$ -Si/ $n^+$ -Si junctions fabricated by using SAB. TEM observations of the vicinities of the bonding interfaces of the n-Si/n-Si junctions, indicated a transition layer is likely to be formed by the Ar plasma irradiation in the surface activation process. In EDS measurements, we observed no evidence of oxide layers at the bonding interfaces. The measurements of I-V and  $I/C^2-V$  characteristics of the p-Si/n-Si and  $p^-$ -Si/ $n^+$ -Si junctions revealed that the states at the bonding interfaces, likely to be formed in the transition layer during the surface activation process, had a more marked impact on the electrical properties in the p-Si/n-Si junctions. The carrier transport properties for the reverse-biased p-Si/n-Si and  $p^-$ -Si/ $n^+$ -Si junctions can be explained by using the trap-assisted tunneling model and the Frenkel-Poole model, respectively. The difference in the electrical properties between the p-Si/n-Si and  $p^-$ -Si/ $n^+$ -Si junctions might be related to their depletion layer thicknesses. Furthermore, the impact of the interface states on the electrical properties of the *n*-Si/*n*-Si junctions was found to be small.

#### **ACKNOWLEDGMENTS**

This work was supported by the "Creative research for clean energy generation using solar energy" project in the Core Research for Evolutional Science and Technology (CREST) programs of the Japan Science and Technology Agency (JST).

<sup>&</sup>lt;sup>1</sup>S. Bengtsson and O. Engström, J. Appl. Phys. **66**, 1231 (1989).

<sup>&</sup>lt;sup>2</sup>T. Abe, T. Takei, A. Uchiyama, K. Yoshizawa, and Y. Nakazato, Jpn. J. Appl. Phys., Part 2 29, L2311 (1990).

<sup>&</sup>lt;sup>3</sup>W. P. Maszara, G. Goetz, A. Caviglia, and J. B. Mckitterick, J. Appl. Phys. **64**, 4943 (1988).

<sup>&</sup>lt;sup>4</sup>Y. C. Zhou, Z. H. Zhu, D. Crouse, and Y. H. Lo, Appl. Phys. Lett. **73**, 2337 (1998).

- <sup>5</sup>H. Wada and T. Kamijoh, Jpn. J. Appl. Phys., Part 1 **37**, 1383 (1998).

- <sup>6</sup>F. Shi, K.-L. Chang, J. Epple, C.-F. Xu, K. Y. Cheng, and K. C. Hsieh, J. Appl. Phys. 92, 7544 (2002).

- <sup>7</sup>H. Wada, Y. Ogawa, and T. Kamijoh, Appl. Phys. Lett. **62**, 738 (1993). <sup>8</sup>K. Tanabe, A. F. I. Morral, H. A. Atwater, D. J. Aiken, and M. W.

- Wanlass, Appl. Phys. Lett. 89, 102106 (2006).

- <sup>9</sup>O. Engstrom, S. Bengtsson, G. I. Andersson, and M. O. Andersson, J. Electrochem. Soc. 139, 3638 (1992).

- <sup>10</sup>Q. Y. Tong, E. Schmidt, U. Gosele, and M. Reiche, Appl. Phys. Lett. 64, 625 (1994).

- <sup>11</sup>O. Moutanabbir and U. Gösele, Annu. Rev. Mater. Res. 40, 469 (2010).

- <sup>12</sup>R. H. Esser, K. D. Hobart, and F. J. Kub, J. Electrochem. Soc. 151, G387

- <sup>13</sup>H. Takagi, K. Kikuchi, R. Maeda, T. R. Chung, and T. Suga, Appl. Phys. Lett. 68, 2222 (1996).

- <sup>14</sup>N. Shigekawa, N. Watanabe, and E. Higurashi, in *Proceedings of the 3rd* International IEEE workshop on Low temperature Bonding for 3D Intergration, Tokyo, Japan, 22-23 May 2012, edited by T. Suga, H. Takagi, and E. Higurashi (2012), pp. 109-112.

- <sup>15</sup>M. M. R. Howlader, H. Okada, T. H. Kim, T. Itoh, and T. Suga, J. Electrochem. Soc. 151, G461 (2004).

- <sup>16</sup>H. Takagi and R. Maeda, J. Micromech. Microeng. **15**, 290 (2005).

- <sup>17</sup>M. M. R. Howlader, T. Watanabe, and T. Suga, J. Appl. Phys. 91, 3062 (2002).

- <sup>18</sup>J. Liang, T. Miyazaki, M. Morimoto, S. Nishida, N. Watanabe, and N. Shigekawa, Appl. Phys. Express 6, 021801 (2013).

- <sup>19</sup>S. Essig and F. Dimroth, ECS J. Solid State Sci. Technol. 2, Q178 (2013).

- <sup>20</sup>S. Essig, O. Moutanabbir, A. Wekkeli, H. Nahme, E. Oliva, A. W. Bett, and F. Dimroth, J. Appl. Phys. 113, 203512 (2013).

- <sup>21</sup>S. E. Swirhun, J. A. del Alamo, and R. M. Swanson, IEEE Electron Device Lett. 7, 168 (1986).

- <sup>22</sup>J. A. del Alamo, S. E. Swirhun, and R. M. Swanson, Solid-State Electron. 28, 47 (1985).

- <sup>23</sup>M. J. Jackson, B. L. Jackson, and M. S. Goorsky, J. Appl. Phys. 110, 104903 (2011).

- <sup>24</sup>J. T. Torvik, C. Qiu, M. Leksono, and J. I. Pankove, Appl. Phys. Lett. **72**, 945 (1998).

- <sup>25</sup>E. Danielsson, C. M. Zetterling, M. Östling, A. Nikolaev, I. P. Nikitina, and V. Dmitriev, IEEE Trans. Electron Devices 48, 444 (2001).

- <sup>26</sup>O. Mitrofanov and M. Manfra, Appl. Phys. Lett. **84**, 422 (2004).

- <sup>27</sup>J. P. Donnelly and A. G. Milnes IEEE Trans. Electron Devices 14, 63

- <sup>28</sup>C. Lian, H. G. Xing, Y. Chang, and N. Fichtenbaum, Appl. Phys. Lett. 93, 112103 (2008).

- <sup>29</sup>E. Arslan, S. Bütün, and E. Ozbay, Appl. Phys. Lett. **94**, 142106 (2009).

- <sup>30</sup>H. Zhang, E. J. miller, and E. T. Yu, J. Appl. Phys. **99**, 023703 (2006).

- <sup>31</sup>L. Sang, M. Liao, N. Ikeda, Y. Koide, and M. Sumiya, Appl. Phys. Lett. **99**, 161109 (2011).

- <sup>32</sup>C. T. Sah, R. N. Noyce, and W. Shockley, Proc. IRE **45**, 1228 (1957).

- <sup>33</sup>R. B. Fair and H. W. Wivell, *IEEE Trans. Electron Devices* **23**, 512 (1976).

- <sup>34</sup>L. W. Sang, M. Y. Liao, Y. Koide, and M. Sumiya, Appl. Phys. Lett. 99, 031115 (2011).