## Effects of thermal annealing process on the electrical properties of p+-Si/n-SiC heterojunctions

Jianbo Liang, S. Nishida, T. Hayashi, M. Arai and Naoteru Shigekawa

| Citation    | Applied Physics Letters, 104(16): 161604                                                                                                                                                                                                                                                                            |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Issue Date  | 2014-4                                                                                                                                                                                                                                                                                                              |

| Туре        | Journal Article                                                                                                                                                                                                                                                                                                     |

| Textversion | publisher                                                                                                                                                                                                                                                                                                           |

| Rights      | This article may be downloaded for personal use only. Any other use requires prior permission of the author and AIP Publishing.  The following article appeared in Applied Physics Letters 104, 161604 (2014) and may be found at <a href="https://doi.org/10.1063/1.4873113">https://doi.org/10.1063/1.4873113</a> |

| DOI         | 10.1063/1.4873113                                                                                                                                                                                                                                                                                                   |

Self-Archiving by Author(s)

Placed on: Osaka City University Repository

LIANG J., NISHIDA S., HAYASHI T., SHIGEKAWA N., & ARAI M. (2014). Effects of thermal annealing process on the electrical properties of p+-Si/n-SiC heterojunctions. Applied Physics Letters. 10,161604.

## Effects of thermal annealing process on the electrical properties of p<sup>+</sup>-Si/n-SiC heterojunctions

J. Liang, S. Nishida, M. Arai, and N. Shigekawa

Citation: Appl. Phys. Lett. 104, 161604 (2014); doi: 10.1063/1.4873113

View online: http://dx.doi.org/10.1063/1.4873113

View Table of Contents: http://aip.scitation.org/toc/apl/104/16

Published by the American Institute of Physics

## Articles you may be interested in

Surface activated bonding of silicon wafers at room temperature Applied Physics Letters **68**, 2222 (1998); 10.1063/1.115865

Electrical properties of Si/Si interfaces by using surface-activated bonding Journal of Applied Physics **114**, 183703 (2013); 10.1063/1.4829676

Realization of direct bonding of single crystal diamond and Si substrates Applied Physics Letters **110**, 111603 (2017); 10.1063/1.4978666

Effects of interface state charges on the electrical properties of Si/SiC heterojunctions Applied Physics Letters **105**, 151607 (2014); 10.1063/1.4898674

Characterization of the bonding strength and interface current of p-Si/n-InP wafers bonded by surface activated bonding method at room temperature

Journal of Applied Physics 91, 3062 (2002); 10.1063/1.1430883

Bonding of silicon wafers for silicon-on-insulator Journal of Applied Physics **64**, 4943 (1998); 10.1063/1.342443

## Effects of thermal annealing process on the electrical properties of p<sup>+</sup>-Si/n-SiC heterojunctions

J. Liang, <sup>1,a)</sup> S. Nishida, <sup>1</sup> M. Arai, <sup>2</sup> and N. Shigekawa <sup>1</sup>

<sup>1</sup>Department of Electrical Engineering, Osaka City University, 3-3-138 Sugimoto, Sumiyoshi, Osaka 558-8585, Japan

<sup>2</sup>New Japan Radio Co., Ltd., Fukuoka 2-1-1, Fujimino, Saitama 356-8510, Japan

(Received 21 February 2014; accepted 11 April 2014; published online 22 April 2014)

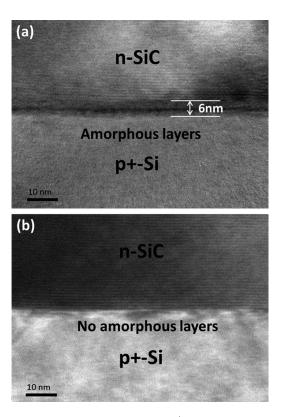

The effects of thermal annealing process on the interface in p<sup>+</sup>-Si/n-SiC heterojunctions fabricated by using surface-activated bonding are investigated. It is found by measuring their current-voltage (*I-V*) characteristics that the reverse-bias current and the ideality factor decreased to  $2.98 \times 10^{-6} \,\mathrm{mA/cm^2}$  and 1.03, respectively, by annealing the junctions at  $1000\,^{\circ}\mathrm{C}$ . Observation by using transmission electron microscopy indicates that an amorphous layer with a thickness of  $\sim 6 \,\mathrm{nm}$  is formed at the unannealed interface, which vanishes after annealing at  $1000\,^{\circ}\mathrm{C}$ . No structural defects at the interface are observed even after annealing at such a high temperature. © 2014 *AIP Publishing LLC*. [http://dx.doi.org/10.1063/1.4873113]

Silicon carbide (SiC) has been extensively studied for high-power electronics application because of its unique physical properties, such as a wide band gap, high thermal conductivity, high electron saturation velocity, high physical, chemical stability, and high breakdown field. The combination of SiC with Si technologies hold the promise for opening up electronic applications in areas requiring high-frequency operation, high power, and high temperature environments. Growth of SiC on Si to form heterojunctions is of considerable interest in realizing wide band gap emitters or window regions in bipolar transistors,<sup>2</sup> photo-detectors, and electroluminescence devices.<sup>3</sup> However, the large lattice mismatch between Si and SiC has limited their intrinsic performance. 4 It is found that growth of SiC layers on Si substrates results in junctions with low breakdown voltage, and high reverse-bias current, 5-7 possibly due to the low-temperature growth of SiC films. One way to overcome these difficulties is direct wafer bonding which can accommodate the lattice mismatch between the bonding substrates. In the process of direct wafer bonding, however, thermal annealing at high temperatures is required so as to achieve enough bonding strength. There are a few literatures which have reported for direct wafer bonding-based Si/SiC heterojunctions<sup>8-11</sup> and Si/6H-SiCbased MOSFETs devices. 12 The influences of annealing process on the electrical and structural behaviors of the Si/SiC heterojunctions have not yet been reported. An alternative approach to achieve Si/SiC heterojunctions with high mechanical strength can be realized by using surface-activated bonding (SAB). SAB, in which surfaces of substrates are activated by the fast atom beams of Ar prior to bonding, has enabled us to bond substrates without annealing. 13-17

In this work, we studied the effects of thermal annealing process on the electrical properties of  $p^+$ -Si/n-SiC heterojunction. The electrical properties of the  $p^+$ -Si/n-SiC junctions without annealing and after annealing were investigated by measuring their current-voltage (I-V) characteristics. The structural properties of the interfaces were examined by transmission electron microscopy (TEM) observation. The

B-doped (100) p<sup>+</sup>-Si substrate and n-4H-SiC epitaxial substrates  $(6 \,\mu\text{m}, \sim 5 \times 10^{15} \,\text{cm}^{-3})$  epitaxial layer/0.5  $\mu$ m,  $>1 \times 10^{18} \, \mathrm{cm}^{-3}$  buffer layer/substrate  $\sim 3 \times 10^{18} \, \mathrm{cm}^{-3}$ ) were used for the bonding experiment. The Hall measurements at room temperature revealed that the resistivity and carrier concentration were 0.003  $\Omega$ ·cm and  $2.6 \times 10^{19}$  cm<sup>-3</sup> for the p<sup>+</sup>-Si substrates, respectively. Before bonding, Al/Ni/Au multilayers were evaporated on the backside of three n-SiC substrates. The ohmic contacts of n-SiC substrates were formed by a rapid thermal annealing at 1000 °C for 60 s in N<sub>2</sub> gas ambient. These substrates and three p<sup>+</sup>-Si substrates were bonded to each other by using SAB. 15-17 And then, the bonded samples were annealed separately at 400, 700, and 1000 °C for 60 s in N<sub>2</sub> gas ambient. After the bonding, Al/Ni/Au multilayers were evaporated on the backside of p<sup>+</sup>-Si substrates, and ohmic contacts were achieved by annealing them at 400 °C for 60 s. Another bonding sample was fabricated by forming ohmic contacts on each of n-SiC and p<sup>+</sup>-Si substrates and bonding them. The characteristics of this sample were investigated while the junction was unannealed. All of the four bonded samples were diced into 4 mm<sup>2</sup> pieces. We measured their *I-V* characteristics using an Agilent B2902A Precision Measurement Unit. The bonding interfaces of the p<sup>+</sup>-Si/n-SiC junctions were investigated using TEM (JEOL JEM-2100).

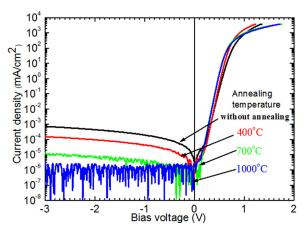

The I-V characteristics measured at room temperature are shown in Fig. 1. A hump is observed in the I-V characteristics of the unannealed junction at low forward-bias voltages. The hump becomes much smaller after annealing at  $400\,^{\circ}\text{C}$ . It disappeared when the junctions were annealed at temperatures above  $700\,^{\circ}\text{C}$ . The ideality factor for the forward bias voltages between 0.2 and 0.5 V was extracted to be 1.32, 1.15, 1.1, and 1.0 for the unannealed junction and junctions annealed at  $400,\,700,\,$  and  $1000\,^{\circ}\text{C},\,$  respectively. The magnitude of the current increased as the junctions were more deeply reverse biased. Furthermore, as the annealing temperature increased, the magnitude of the reverse-bias current at  $-3\,\text{V}$  decreased significantly from  $7.20\times10^{-4}$  to

applicability of Si/SiC heterojunctions for functional devices was explored based on these measurements.

a)E-mail: liang@elec.eng.osaka-cu.ac.jp

FIG. 1. *I-V* characteristics of  $p^+$ -Si/n-SiC junctions without being annealed and annealed at 400, 700, and 1000 °C measured at room temperature.

$2.98 \times 10^{-6}$  mA/cm<sup>2</sup>. The series resistance of the junctions was extracted from the slope of the measured *I-V* characteristics for the forward bias voltages between 0.8 and 1.7 V. We found that the resistance increased after annealing above 700 °C, which is attributed to the oxidation of the evaporated metal for the higher annealing process. We also found that the turn-on voltage of the junctions, which was defined as the forward-bias voltage for the current of  $100 \, \text{mA/cm}^2$ , decreased from 0.78 to 0.68 V as the annealing temperature increased. The values of parameters for the respective junctions are summarized in Table I.

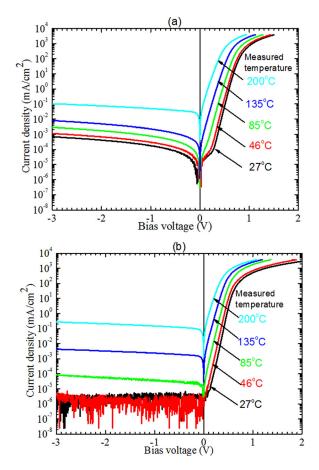

The I-V characteristics of the unannealed junction and the junction annealed at  $1000\,^{\circ}\text{C}$  measured at various temperatures are shown in Figs. 2(a) and 2(b), respectively. We find that the slope of the current obtained at 85, 135, and  $200\,^{\circ}\text{C}$  after annealing at  $1000\,^{\circ}\text{C}$  for reverse bias voltages between -1 and  $-3\,\text{V}$  is not sensitive to the temperature of measurement. In comparison, the slope of the current for the unannealed junction decreases as the temperature of measurement increases.

Figures 3(a) and 3(b) show TEM images of the unannealed interface and the interface annealed at  $1000\,^{\circ}$ C, respectively. An amorphous layer of  $\sim 6\,\mathrm{nm}$  thickness was formed at the interface without annealing. After annealing at  $1000\,^{\circ}$ C, an abrupt interface and no amorphous layer are observed at the interface. More importantly, no structural defects such as cracks were observed at the interface whether with or without annealing.

Prior to bonding, the surfaces were irradiated by the fast atom beam of Ar in the SAB process, so that the surface states are likely to be formed at the interface. 15–17 Such surface states should be distributed in the 6 nm thick amorphous

TABLE I. The reverse-bias current, turn-on voltage, ideality factor, and resistance of  $p^+$ -Si/n-SiC junctions.

| Annealing temperature | Reverse-bias current (mA/cm <sup>2</sup> ) | Turn-on<br>voltage (V) | Ideality<br>factor | Resistance $(\Omega \cdot cm^2)$ |

|-----------------------|--------------------------------------------|------------------------|--------------------|----------------------------------|

| Without annealing     | $7.20 \times 10^{-4}$                      | 0.78                   | 1.32               | 0.13                             |

| 400 °C                | $1.56 \times 10^{-4}$                      | 0.71                   | 1.15               | 0.10                             |

| 700°C                 | $1.30 \times 10^{-5}$                      | 0.67                   | 1.10               | 0.28                             |

| 1000 °C               | $2.98 \times 10^{-6}$                      | 0.68                   | 1.03               | 0.25                             |

FIG. 2. I-V characteristics of p $^+$ -Si/n-SiC junctions without being annealed (a) and annealed at  $1000\,^{\circ}$ C (b) measured at various temperatures.

FIG. 3. TEM cross-section images of the  $p^+$ -Si/n-SiC interface without being annealed (a) and annealed at  $1000\,^{\circ}$ C (b).

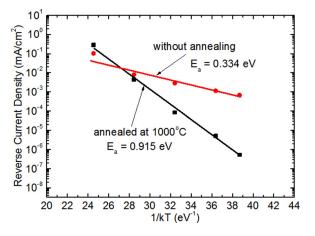

layer [Fig. 3(a)]. In the I-V characteristic of  $p^+$ -Si/n-SiC junction without annealing the magnitude of the reverse-bias current increases with increasing the bias voltage and the temperature of the measurement, similar to SAB-based p<sup>-</sup>-Si/n<sup>+</sup>-Si junctions<sup>16</sup> and wafer-fused p-GaAs/n-GaN heterojunctions. <sup>18</sup> The relationship between the reverse-bias current at -3 V and the temperature of the measurement is shown in Fig. 4. The data obtained at 27 and 46 °C are not shown in this figure because they are below the resolution of the measurement unit. We found that the reverse-bias current dependence on the temperature was approximately expressed as  $I \propto \exp(-E_a/kT)$ , where  $E_a$  is the activation energy. The value of the activation energy was estimated to be 0.33 and 1.02 eV for the unannealed junction and junction annealed at 1000 °C, respectively.

The bias voltage and the temperature dependence of the reverse-bias current suggest that in the unannealed junctions, current generation is occurring via a two-step process at the Si/SiC interface. First, the electrons in the valence band edge of p<sup>+</sup>-Si were thermally excited to the interface states. Then, the electrons tunnel into the conduction band of the n-SiC. The features in the p<sup>+</sup>-Si/n-SiC junction after annealing at 1000 °C—such as the disappearance of the amorphous layer, and the decrease of the ideality factor to 1.03—indicated that the effects of the interface states are negligible and the diffusion current mechanism dominates the transport properties of carriers across the interface for the forward bias voltages.

The existence of amorphous layer across the unannealed interface is assumed to prohibit fracturing caused by the difference in lattice constants between Si and SiC. Neither amorphous layer nor structural defects were observed at the interface after annealing at 1000 °C, which means that the amorphous layer of the p<sup>+</sup>-Si/n-SiC interface was recrystallized due to such a high-temperature annealing process. Similar change in the structure of the interface was observed in the p-Si/n-GaAs and p-GaP/n-GaAs heterojunctions fabricated by SAB. 19,20 The reduced amorphous layer thickness upon annealing is assumed to be responsible for the observed improvement of the *I-V* characteristics after annealing. We find that the magnitude of the reverse-bias current for higher annealing temperatures much smaller than those previously reported for n-Si/n-SiC (Ref. 21) and p-Si/n-SiC (Ref. 10)

FIG. 4. Relationship of the reverse-bias current measured at -3 V for  $p^+\text{-Si/n-SiC}$  junctions without being annealed and annealed at 1000  $^\circ\text{C}$  .

heterojunctions fabricated by molecular beam epitaxy or by direct wafer bonding.

Given that the high temperature (typically 1000 °C)<sup>22,23</sup> process is required for forming good ohmic contacts on SiC, it is notable that the two substrates were firmly bonded to each other after annealing at 1000 °C. It is also noteworthy that that (1) the reverse-bias current at -3 V decreased to  $2.98 \times 10^{-6} \,\mathrm{mA/cm^2}$  and (2) the amorphous layer vanished after annealing at 1000 °C, which suggest that the SAB-based Si/SiC junctions are anticipated to play a significant role in fabricating devices operating for high-power and high-frequency applications.

In summary, we fabricated the p<sup>+</sup>-Si/n-SiC junctions using the SAB and demonstrated the influence of thermal annealing process on the interface. The reverse-bias current at  $-3 \,\mathrm{V}$  and the ideality factor were reduced to  $2.98 \times 10^{-6} \,\mathrm{mA/cm^2}$  and 1.03, respectively, after annealing at 1000 °C. An amorphous layer with thickness of ~6 nm, which was observed at the unannealed interface, disappeared after annealing at 1000 °C. Thus, the SAB technology in combination with the thermal annealing is likely to be useful for fabricating devices for high-power applications in harsh environments.

This work was supported by "Creative Research for Clean Energy Generation Using Solar Energy" project in Core Research for Evolutional Science and Technology (CREST) programs of the Japan Science and Technology Agency (JST).

<sup>1</sup>J. Scofield, H. Kosai, B. Jordan, S.-H. Ryu, S. Krishnaswami, F. Husna, and A. Agarwal, in Proceedings of the European Conference on Silicon Carbide and Related Materials (ECSCRM 2006) (2007), p. 556.

<sup>2</sup>H. Kroemer, Proc. IEEE **70**, 13 (1982).

<sup>3</sup>K.-H. Wu, Y.-K. Fang, J.-H. Zhou, and J.-J. Ho, Jpn. J. Appl. Phys. 36, 5151 (1997)

<sup>4</sup>A. N. Nazarov, Ya. N. Vovk, V. S. Lysenko, V. I. Turchanikov, V. A. Scryshevskii, and S. Ashok, J. Appl. Phys. 89, 4422 (2001).

<sup>5</sup>T. Sugii, T. Ito, Y. Furumura, M. Doki, F. Mieno, and M. Maeda, IEEE Electron Device Lett. 9, 87 (1988).

<sup>6</sup>T. Sugii, T. Aoyama, and T. Ito, J. Electrochem. Soc. **136**, 3111 (1989).

<sup>7</sup>S. Magafas, N. Georgoulas, and A. Thanailakis, Semicond. Sci. Technol. 7, 1363 (1992).

<sup>8</sup>M. R. Jennings, A. Pèrez-Tomás, A. Bashir, A. Sanchez, A. Severino, P. J. Ward, S. M. Thomas, C. Fisher, P. M. Gammon, M. Zabala, S. E. Burrows, B. Donnellan, D. P. Hamilton, D. Walker, and P. A. Mawby, ECS Solid State Lett. 1, P85 (2012).

A. Pèrez-Tomás, M. Lodzinski, O. J. Guy, M. R. Jennings, M. Placidi, J. Llobet, P. M. Gammon, M. C. Davis, J. A. Covington, S. E. Burrows, and P. A. Mawby, Appl. Phys. Lett. 94, 103510 (2009).

<sup>10</sup>M. R. Jennings, A. Pèrez-Tomás, O. J. Guy, R. Hammond, S. E. Burrows, P. M. Gammon, M. Lodzinski, J. A. Covington, and P. A. Mawby, Electrochem. Solid-State Lett. 11, H306 (2008).

<sup>11</sup>P. M. Gammon, A. Perez-Tomás, M. R. Jennings, A. M. Sanchez, C. Fisher, S. T. Thomas, B. T. Donnellan, and P. A. Mawby, Mater. Sci. Forum 740-742, 1006 (2013).

<sup>12</sup>M. Yoshimoto, R. Araki, T. Kurumi, and H. Kinoshita, ECS Trans. 50, 61 (2013).

<sup>13</sup>H. Takagi, K. Kikuchi, R. Maeda, T. R. Chung, and T. Suga, Appl. Phys. Lett. 68, 2222 (1996).

<sup>14</sup>M. M. R. Howlader, T. Watanabe, and T. Suga, J. Vac. Sci. Technol., B **19**, 2114 (2001)

<sup>15</sup>N. Shigekawa, N. Watanabe, and E. Higurashi, in *Proceedings of 3rd* International IEEE Workshop on Low-temperature Bonding for 3D Integration, Tokyo, Japan, 2012, p. 109.

<sup>16</sup>J. Liang, T. Miyazaki, M. Morimoto, S. Nishida, N. Watanabe, and N. Shigekawa, Appl. Phys. Express 6, 021801 (2013).

<sup>17</sup>J. Liang, T. Miyazaki, M. Morimoto, S. Nishida, and N. Shigekawa, J. Appl. Phys. 114, 183703 (2013).

- <sup>18</sup>G. Lian, H. G. Xing, Y. Chang, and N. Fichtenbaum, Appl. Phys. Lett. 93, 112103 (2008).

- <sup>19</sup>T. Yu, M. M. R. Howlader, F. Zhang, and M. Bakr, ECS Trans. 35, 3 (2011).

- <sup>20</sup>M. M. R. Howlader, T. Suga, F. Zhang, T. H. Lee, and M. J. Kim, Electrochem. Solid-State Lett. 13, H61 (2010).

- <sup>21</sup>A. Pèrez-Tomás, M. R. Jennings, M. Davis, J. A. Covington, P. A. Mawby V. Shah and T. Grasby J. Appl. Phys. **102**, 14505 (2007).

- Mawby, V. Shah, and T. Grasby, J. Appl. Phys. **102**, 14505 (2007). <sup>22</sup>F. Roccaforte, F. L. Via, V. Raineri, R. Pierobon, and E. Zanoci, J. Appl. Phys. **93**, 9137 (2003).

- <sup>23</sup>E. Danielsson, C.-M. Zetterling, M. Östling, A. Nikolaev, I. P. Nikitina, and V. Dmitriev, IEEE Trans. Electron Devices 48, 444 (2001).